# Biyani's Think Tank

Concept based notes

# Computer Architecture

(MCA)

Shweta Nigam Namarta Mehta

nol Dept. of MCA(Information Technology) Biyani Institute of Science and Management Jaipur

#### Published by:

#### Think Tanks **Biyani Group of Colleges**

Concept & Copyright:

#### ©Biyani Shikshan Samiti

Sector-3, Vidhyadhar Nagar, Jaipur-302 023 (Rajasthan)

Ph: 0141-2338371, 2338591-95 • Fax: 0141-2338007

E-mail: acad@biyanicolleges.org

Website: www.gurukpo.com; www.biyanicolleges.org

Edition: 2011 Price:

take-While every effort is taken to avoid errors or omissions in this Publication, any mistake or omission that may have crept in is not intentional. It may be taken note of that neither the publisher nor the author will be responsible for any damage or loss of any kind arising to anyone in any manner on account of such errors and omissions.

*Leaser Type Settled by :*

**Biyani College Printing Department**

# **Preface** ■

am glad to present this book, especially designed to serve the needs of the students. The book has been written keeping in mind the general weakness in understanding the fundamental concept of the topic. The book is self-explanatory and adopts the "Teach Yourself" style. It is based on question-answer pattern. The language of book is quite easy and understandable based on scientific approach.

The text explained all the concepts of Internet & Intranet are very simple way and according the syllabus of (BCA) graduate level students.

Any further improvement in the contents of the book by making corrections, omission and inclusion is keen to be achieved based on suggestions from the reader for which the author shall be obliged.

I acknowledge special thanks to Mr. Rajeev Biyani, *Chairman* & Dr. Sanjay Biyani, *Director (Acad.)* Biyani Group of Colleges, who is the backbone and main concept provider and also have been constant source of motivation throughout this endeavor. We also extend our thanks to Biyani Sikhshan Samiti, Jaipur, who played an active role in co-coordinating the various stages of this endeavor and spearheaded the publishing work.

I look forward to receiving valuable suggestions from professors of various educational institutions, other faculty members and the students for improvement of the quality of the book. The reader may feel free to send in their comments and suggestions to the under mentioned address.

Author

## **Syllabus**

Logic gates, basic combinational logic, multiplexer, decoders, encoders comparators, adder and subtracters, BCD to 7 segment decoder, sequential circuits, RS, JK, D and T flip flops, counter and shift register, programmable logic array (PLA), programmable logic device (PLD).

Addressing methods and machine program sequencing-memory locations addresses, encoding of information, instructions and instructions sequencing, addressing modes, paging, relative, indirect and indexed addressing.

Basics of Computer organization: System buses and instruction cycles, memory subsystem organization and interfacing, I/O subsystem organizations and interfacing, Register transfer languages.

CPU design: Specifying a CPU, design and implementation of a simple CPU (fetching instructions from memory, decoding and executing instructions, establishing required data paths, design of ALU, design of the control unit and design verification), design and implementation of a simple micro-sequencer.

Memory systems, virtual and cache memory.

Input and Output organization: Asynchronous data transfer, programmed I/O Interrupts (types, processing of interrupts implementing interrupts inside CPU) Direct memory access, I/O processors, serial communication.

# **Contents**

| S.No | Chapter Name               |

|------|----------------------------|

| 1    | Combinational Circuits     |

| 2    | Sequential Circuits        |

| 3    | Register                   |

| 4    | I/O Interface              |

| 5    | Instruction and Addressing |

| 6    | Arithmetic/Logic unit      |

| 7    | Memory                     |

| 8    | Processor                  |

| 9    | Microprocessor             |

| 10   | Microprocessor program     |

## Chapter 1

## **Combinational Circuits**

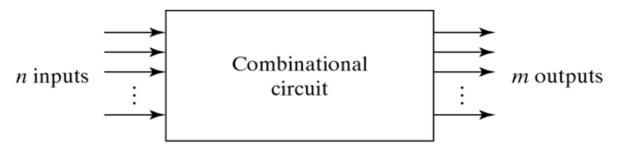

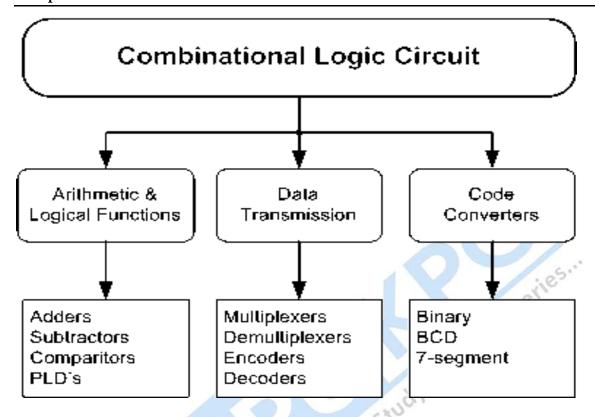

#### Q1. Define Combinational Circuits.

Ans. Combinational Logic Circuits are made up from basic logic NAND, NOR or NOT gates that are "combined" or connected together to produce more complicated switching circuits. These logic gates are the building blocks of combinational logic circuits. An example of a combinational circuit is a decoder, which converts the binary code data present at its input into a number of different output lines, one at a time producing an equivalent decimal code at its output.

Block Diagram of Combinational Circuit

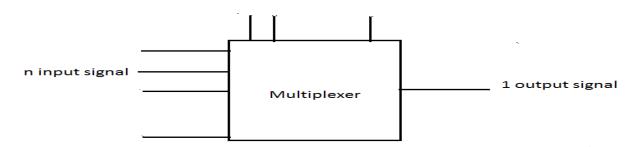

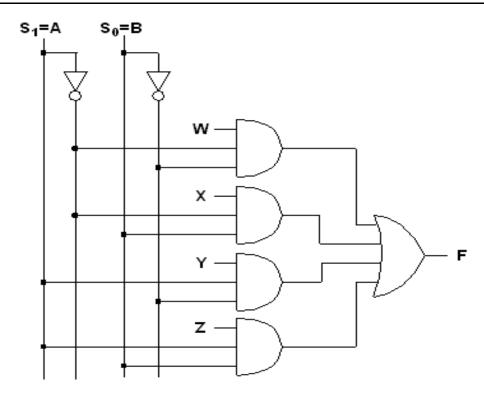

# Q2. Define Multiplexer .Draw 4X1 MUX.

Ans. A multiplexer or mux is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. A multiplexer of 2<sup>n</sup> inputs has n select lines, which are used to select which input line to send to the output. Multiplexers are mainly used to increase the amount of data that can be sent over the network within a certain amount of time and bandwidth.

$F = \overline{AB}W + \overline{ABX} + A\overline{BY} + ABZ$

#### Truth table of 4 to 1 MUX

|            | •         | 21077 - 21007 - 2107 |

|------------|-----------|----------------------|

|            |           | (o                   |

| MUX        | Access to |                      |

| Data selec | t inputs  | Outputs              |

| S1         | S0        | F                    |

| 0          | 0         | W                    |

| 0          | 1         | X                    |

| 1          | 0         | Y                    |

| 1          | 1         | Z                    |

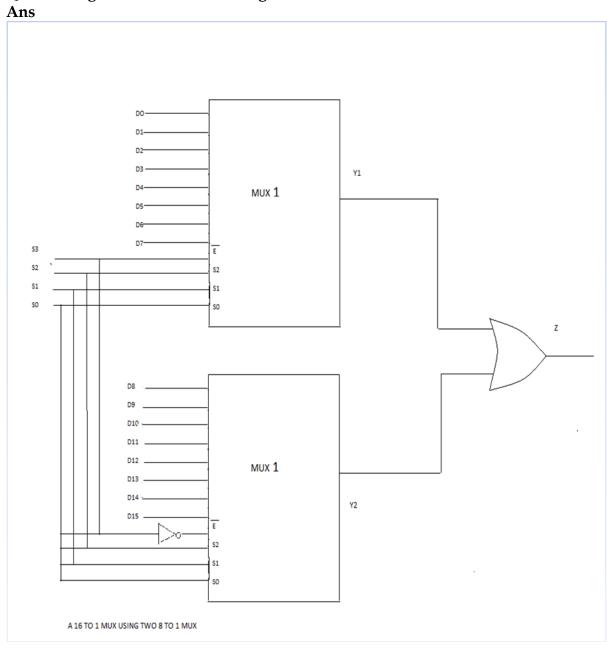

## Q3. Design a 16- to -1 MUX using two 8 - to -1 MUX

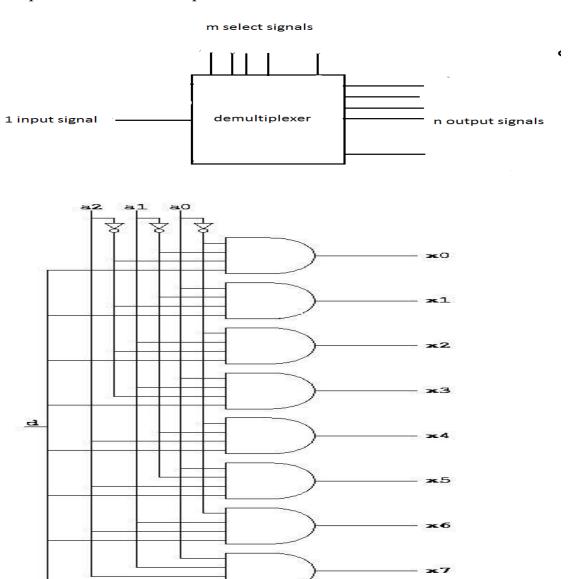

#### Q4. Define Demultiplexer .Along with 1X8 Demux.

**Ans**. The demultiplexer is the inverse of the multiplexer, in that it takes a single data input and n address inputs. It has 2n outputs. The address input determine which data output is going to have the same value as the data input. The other data outputs will have the value 0.

#### 1 TO 8 DMUX

#### Truth table of 1 to 8 DEMUX

| a2 a1 a0 d   x7 | x6 | x5 | x4 | <b>x</b> 3 | x2 | <b>x</b> 1 | <b>x</b> 0 |

|-----------------|----|----|----|------------|----|------------|------------|

|                 |    |    |    | -          |    |            |            |

| 0 0 0 c   0     | 0  | 0  | 0  | 0          | 0  | 0          | C          |

| 0 0 1 c   0     | 0  | 0  | 0  | 0          | 0  | C          | 0          |

| 0 1 0 c   0     | 0  | 0  | 0  | 0          | C  | 0          | 0          |

| 0 1 1 c   0     | 0  | 0  | 0  | C          | 0  | 0          | 0          |

| 1 0 0 c   0     | 0  | 0  | C  | 0          | 0  | 0          | 0          |

| 101c   0        | 0  | C  | 0  | 0          | 0  | 0          | 0          |

| 1 1 0 c   0     | C  | 0  | 0  | 0          | 0  | 0          | 0          |

| 111c c          | 0  | 0  | 0  | 0          | 0  | 0          | 0          |

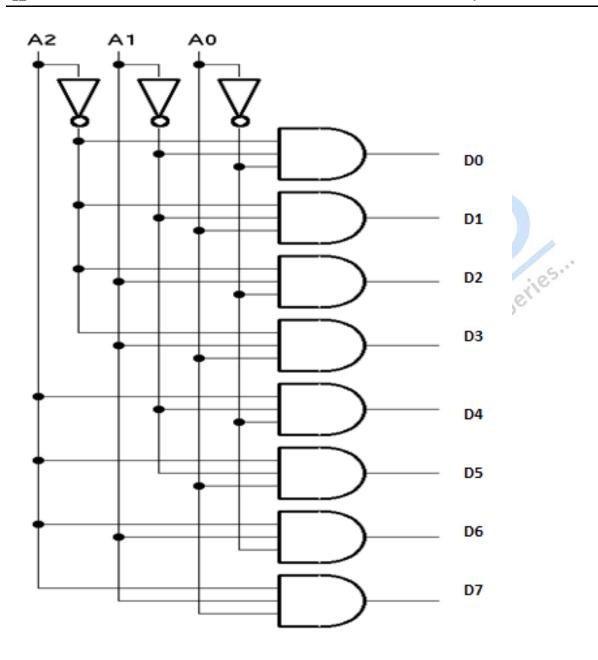

#### Q5. Explain 3X8 Decoder. And give its application.

Ans. Is a combinational circuit that converts binary information from n input lines to a maximum of  $2^n$  unique output lines For example if the number of input is n=3 the number of output lines can be  $m=2^3$ .

#### Truth table for binary to octal

|       | Inputs | ;     |       |                |       | Out   | puts  |       |       |       |

|-------|--------|-------|-------|----------------|-------|-------|-------|-------|-------|-------|

| $A_2$ | $A_1$  | $A_0$ | $D_7$ | $D_{\epsilon}$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $D_0$ |

| ×     | ×      | ×     | 0     | 0              | 0     | 0     | 0     | 0.    | 0     | 0     |

| 0     | 0      | 0     | 0     | 0              | 0     | 0     | .0    | 0     | :0    | 1     |

| 0     | 0      | 1     | 0     | 0              | 0     | 0     | 0     | 0     | 1     | 0     |

| 0     | 1      | 0     | 0     | 0              | 0     | 0     | 0     | 1     | 0     | 0     |

| 0     | 1      | 1     | 0     | 0              | 0     | 0     | 1     | 0     | 0     | 0     |

| 1     | 0      | 0     | 0     | 0              | 0     | 1     | 0     | 0     | 0     | 0     |

| 1     | 0      | 1     | 0     | 0              | 1     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1      | 0     | 0     | 1              | 0     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1      | 1.    | 1     | 0              | 0     | 0     | 0     | 0     | 0     | 0     |

#### **Applications**

- 1. They are used in counter systems.

- 2. They are used in analog to digital converters

- 3. Decoder output can be used to drive a display system

### Q6. What are the applications of Multiplexer?

**Ans**. These circuits use mostly find in numerous and varied applications in digital systems of all types such as **data selection**, **data routing**, **operation sequencing**, **parallel-to-serial conversion**.

#### **Application areas**

- 1. Telephony

- 2. Video processing

- 3. Digital broadcasting

- 4. Analog broadcasting

#### Q7. Explain Encoder.

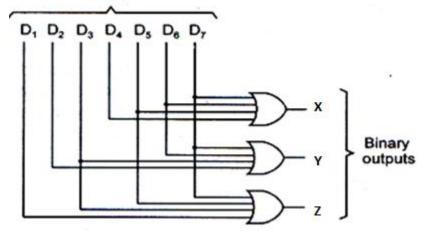

Ans. An encoder is a digital function that produces a reverse operation from that of a decoder. An encoder has 2<sup>n</sup>(or less) input lines and n output lines. The output lines generate the binary code for the  $2^n$  input variables.

Octal -to-Binary Encoder

|    |     |     | in  | put  | s   |     |      | οι | ıtpu | ıts |      |

|----|-----|-----|-----|------|-----|-----|------|----|------|-----|------|

| Do | ) D | 1 D | 2 D | 3 D  | 4 D | 5 D | 6 D7 | х  | у    | z   |      |

| 1  | 0   | 0   | 0   | 0    | 0   | 0   | 0    | 0  | 0    | 0   |      |

| 0  | 1   | 0   | 0   | 0    | 0   | 0   | 0    | 0  | 0    | 1   |      |

| 0  | 0   | 1   | 0   | 0    | 0   | 0   | 0    | 0  | 1    | 0   |      |

| 0  | 0   | 0   | 1   | 0    | 0   | 0   | 0    | 0  | 1    | 1   |      |

| 0  | 0   | 0   | 0   | 1    | 0   | 0   | 0    | 1  | 0    | 0   |      |

| 0  | 0   | 0   | 0   | 0    | 1   | 0   | 0    | 1  | 0    | 1   |      |

| 0  | 0   | 0   | 0   | 0    | 0   | 1   | 0    | 1  | 1    | 0   | 1    |

| 0  | 0   | 0   | 0   | 0    | 0   | 0   | 1    | 1  | 1    | 1   | 4611 |

|    |     | 0   | cta | l in | put | S   |      |    |      |     |      |

#### Q8 Define Programmable Logic Devices (PLDs)

**Ans.** An IC that contains large numbers of gates, flip-flops, etc. that can be configured by the user to perform different functions is called a Programmable Logic Device (PLD).

The internal logic gates and/or connections of PLDs can be changed/configured by a programming process

#### Q9. What are the types of PLDs?.Explain.

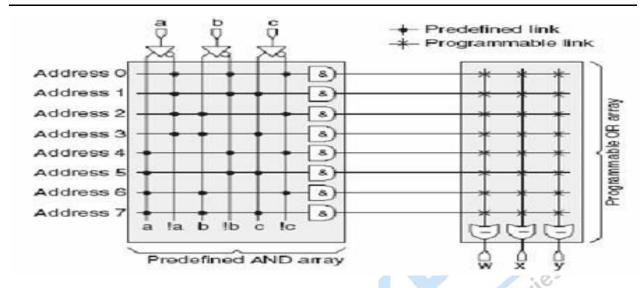

**Ans.** The three fundamental types of PLDs differ in the placement of programmable connections in the AND-OR arrays.

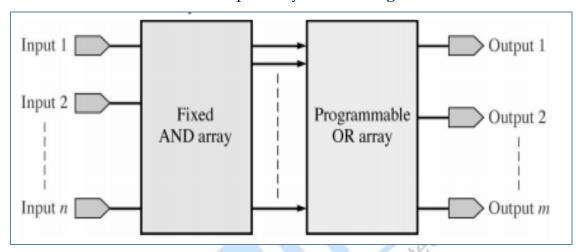

- The PROM (Programmable Read Only Memory) has a fixed AND array (constructed as a decoder) and programmable connections for the output OR gates array. The PROM implements Boolean functions in sum-ofminterms form.

- The PAL (Programmable Array Logic) device has a programmable AND array and fixed connections for the OR array.

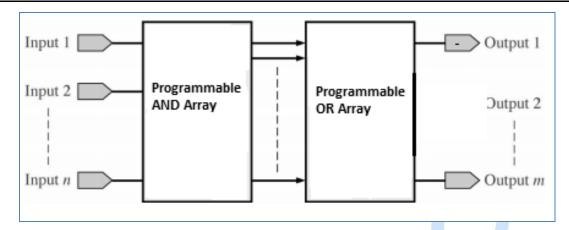

- The PLA (Programmable Logic Array) has programmable connections for both AND and OR arrays. So it is the most flexible type of PLD.

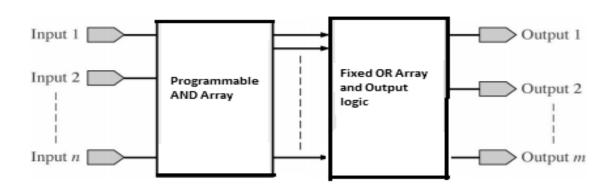

#### Q10. Explain Programmable Logic Array (PLA).

Ans. A programmable logic array (PLA) is a kind of programmable logic device used to implement combinational logic circuits. The PLA has a set of programmable AND gate planes, which link to a set of programmable OR gate planes, which can then be conditionally complemented to produce an output. This layout allows for a large number of logic functions to be synthesized in the sum of products (and sometimes product of sums) canonical forms.

Block diagram of a PLA (programmable logic array)

#### APPLICATION

eries. One application of a PLA is to implement the control over a datapath. It defines various states in an instruction set, and produces the next state (by conditional branching). [eg. if the machine is in state 2, and will go to state 4 if the instruction contains an immediate field; then the PLA should define the actions of the control in state 2, will set the next state to be 4 if the instruction contains an immediate field, and will define the actions of the control in state 4]. Programmable Logic Arrays should correspond to a state diagram for the system. Other commonly used programmable logic devices are PAL, CPLD and FPGA.

#### Q11 Explain Programmable Read-Only Memory(PROM)

The first PLD is PROM was introduced in 1970. PROMs was introduced for use as computer memories in which to store program instructions and constant data values. PROM have fixed AND plane and programmable OR plane. PROM can be use to program any combinational logics with limited numbers of inputs and outputs. Given n variables, it would necessary to have 2n AND gates, one for each possible minterm. A figure below shows the unprogrammed PROM for 3 inputs and 3 outputs, where AND plane is fixed and OR plane is programmable. The programmable links in OR array can be implemented as fused link, or as EPROM transistor or E2PROM cells depend on vendors. PROMs are useful for equations requiring a large number of product terms, but they can support few inputs as every input combination is always decoded and used.

The PROM is used primarily as an addressable memory and not as a logic device because of limitations imposed by fixed AND gates.

Block diagram of a PROM (programmable read-only memory)

#### Q12. Explain the Two basic versions of PROM.

- **Ans. 1) Mask-Programmable:** can be programmed only by the manufacturer. Mask-programmable chip has less delay because connections within the device can be hardwired during manufacture.

- **2) Field-Programmable:** can be programmed by the end-user .Field-programmable chips are less expensive, and can be programmed immediately. The Field Programmable PROM developed into two types, the Erasable Programmable Read-Only Memory (EPROM) and the Electrically Erasable Programmable Read-Only Memory (E2PROM). The E2PROM has the advantage of being erasable and reprogrammable many times.

#### Q.13 Explain Programmable Array Logic (PAL).

Ans. A PLD in which the OR array is fixed (pre-defined) but the AND array is programmable. PAL chips use fuse-programmable logic (i.e., overvoltage is applied to portions of the chip to physically blow a circuit open). It was developed to overcome certain disadvantages of PLA, such as longer delays due to the additional fusible links that result from using two programmable arrays and more difficult complexity.

Block diagram of a PAL (programmable array logic)

## Chapter 2

# **Sequential Circuits**

#### Q1. What is the difference between latch and flip flop.

Ans. latches and flip-flops are the building blocks of sequential circuits.

While gates had to be built directly from transistors, latches can be built from gates, and flip-flops can be built from latches. This fact will make it somewhat easier to understand latches and flip-flops. Both latches and flip-flops are circuit elements whose output depends not only on the current inputs, but also on previous inputs and outputs. The difference between a latch and a flip-flop is that a latch does not have a *clock signal*, whereas a flip-flop always does. Latches are *asynchronous*, which means that the output changes very soon after the input changes. Most computers today, on the other hand, are *synchronous*, which means that the outputs of all the sequential circuits change simultaneously to the rhythm of a global *clock signal*. A *flip-flop* is a synchronous version of the latch.

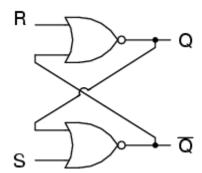

#### Q2. Explain SR LATCH Working.

**Ans.** This latch is called *SR-latch*, which stands for *set* and *reset*.

| S | R | Q     | Q     |

|---|---|-------|-------|

| 0 | 0 | latch | latch |

| 0 | 1 | 0     | 1     |

| 1 | 0 | 1     | 0     |

| 1 | 1 | 0     | 0     |

This latch is called SR-latch, which stands for set and reset.

When S = 0 and R = 0: If we assume Q = 1 and Q' = 0 as initial condition, then output Q after input is applied would be Q = (R + Q')' = 1 and Q' = (S + Q)' = 0. Assuming Q = 0 and Q' = 1 as initial condition, then output Q after the input applied would be Q = (R + Q')' = 0 and Q' = (S + Q)' = 1. So it is clear that when both S and R inputs are LOW, the output is retained as before the application of inputs. (i.e. there is no state change).

When S = 1 and R = 0: If we assume Q = 1 and Q' = 0 as initial condition, then output Q after input is applied would be Q = (R + Q')' = 1 and Q' = (S + Q)' = 0. Assuming Q = 0 and Q' = 1 as initial condition, then output Q after the input applied would be Q = (R + Q')' = 1 and Q' = (S + Q)' = 0. So in simple words when S is HIGH and R is LOW, output Q is HIGH.

When S = 0 and R = 1: If we assume Q = 1 and Q' = 0 as initial condition, then output Q after input is applied would be Q = (R + Q')' = 0 and Q' = (S + Q)' = 1. Assuming Q = 0 and Q' = 1 as initial condition, then output Q after the input applied would be Q = (R + Q')' = 0 and Q' = (S + Q)' = 1. So in simple words when S is LOW and R is HIGH, output Q is LOW.

When S = 1 and R = 1: No matter what state Q and Q' are in, application of 1 at input of NOR gate always results in 0 at output of NOR gate, which results in both Q and Q' set to LOW (i.e. Q = Q'). LOW in both the outputs basically is wrong, so this case is invalid.

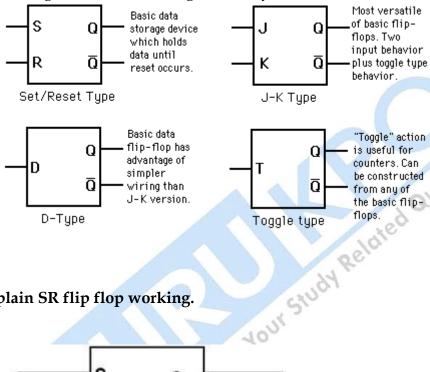

#### Q3. Explain Flip-Flops. Along with its types

Ans. "Flip-flop" is the common name given to two-state devices which offer basic memory for sequential logic operations. Flip-flops are heavily used for digital data storage and transfer and are commonly used in banks called "registers" for the storage of binary numerical data.

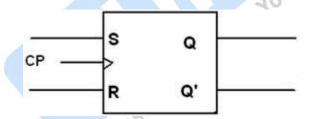

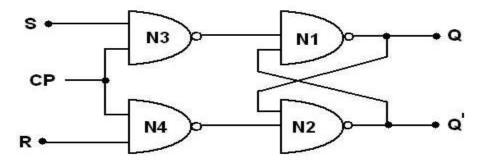

#### O4. Explain SR flip flop working. Ans.

#### **BLOCK DIAGRAM**

The basic flip-flop is a one bit memory cell that gives the fundamental idea of memory device. It constructed using two NAND gates. The two NAND gates N1 and N2 are connected such that, output of N1 is connected to input of N 2 and output of N2 to input of N1. These form the feedback path the inputs are S and R, and outputs are Q and Q'.

#### **LOGIC DIAGRAM**

#### Operation:

- 1. When CP=0 the output of N 3 and N4 are 1 regardless of the value of S and R. This is given as input to N1 and N2. This makes the previous value of Q and Q' unchanged.

- 2. When CP=1 the information at S and R inputs are allowed to reach the latch and change of state in flip-flop takes place.

- 3. CP=1, S=1, R=0 gives the SET state i.e., Q=1, Q'=0.

- 4. CP=1, S=0, R=1 gives the RESET state i.e., Q=0, Q'=1.

- 5. CP=1, S=0, R=0 does not affect the state of flip-flop.

- 6. CP=1, S=1, R=1 is not allowed, because it is not able to determine the next state. This condition is said to be a "race condition".

In the logic symbol CP input is marked with a triangle. It indicates the circuit responds to an input change from 0 to 1. The characteristic table gives the operation conditions of flip-flop. Q (t) is the present state maintained in the flip-flop at time 't'. Q (t+1) is the state after the occurrence of clock pulse.

#### TRUTH TABLE

| S | R | Q (t+1) | Comments      |

|---|---|---------|---------------|

| 0 | 0 | Q t     | No change     |

| 0 | 1 | 0       | Reset / clear |

| 1 | 0 | 1       | Set           |

| 1 | 1 | *       | Not allowed   |

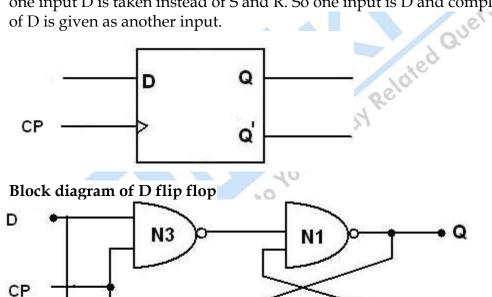

#### Q5. Explain D flip flop.

**Ans.** The D flip-flop is the modified form of R-S flip-flop. R-S flip-flop is converted to D flip-flop by adding an inverter between S and R and only one input D is taken instead of S and R. So one input is D and complement of D is given as another input.

#### **LOGIC DIAGRAM**

When the clock is low both the NAND gates (N1 and N2) are disabled and Q retains its last value. When clock is high both the gates are enabled and the input value at D is transferred to its output Q. D flip-flop is also called "Data flip-flop".

N<sub>2</sub>

N4

#### Truth table

| CP | D | Q              |

|----|---|----------------|

| 0  | х | Previous state |

| 1  | 0 | 0              |

| 1  | 1 | 1              |

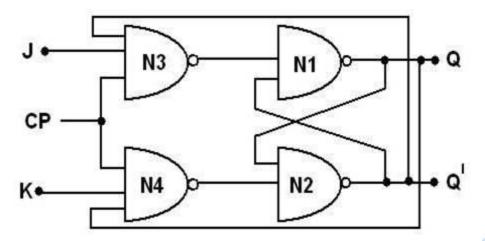

#### Q6. Explain J-K Flip-Flop

The J-K flip-flop is the most versatile of the basic flip-flops. It has the Ans. input- following character of the clocked D flip-flop but has two inputs, the or traditionally labeled J and K. If J and K are different then the output Q takes the value of J at the next clock edge.

#### Block diagram

If J and K are both low then no change occurs. If J and K are both high at the clock edge then the output will toggle from one state to the other. It can perform the functions of the set/reset flip-flop and has the advantage that there are no ambiguous states. It can also act as a T flip-flop to accomplish toggling action if J and K are tied together. This toggle application finds extensive use in binary counters.

The race condition in RS flip-flop, when R=S=1 is eliminated in J-K flip-flop. There is a feedback from the output to the inputs.

the outputs feed back to the enabling NAND gates. This is what gives the toggling action when J=K=1. gives the

#### Truth table

| J | K | Q (t+1 | ) Comments    |

|---|---|--------|---------------|

|   |   |        |               |

| 0 | 0 | Q t    | No change     |

| 0 | 1 | 0      | Reset / clear |

| 1 | 0 | 1      | Set           |

| 1 | 1 | Q' t   | Complement/   |

|   |   |        | toggle.       |

The J and K are called control inputs, because they determine what the flip-flop does when a positive clock edge arrives.

#### Operation:

1. When J=0, K=0 then both N3 and N4 will produce high output and the previous value of Q and Q' retained as it is.

- 2. When J=0, K=1, N3 will get an output as 1 and output of N4 depends on the value of Q. The final output is Q=0, Q'=1 i.e., reset state

- 3. When J=1, K=0 the output of N 4 is 1 and N 3 depends on the value of Q'. The final output is Q=1 and Q'=0 i.e., set state

- 4. When J=1, K=1 it is possible to set (or) reset the flip-flop depending on the current state of output. If Q=1, Q'=0 then N4 passes '0' to N2 which produces Q'=1, Q=0 which is reset state. When J=1, K=1, Q changes to the complement of the last state. The flip-flop is said to be in the toggle state.

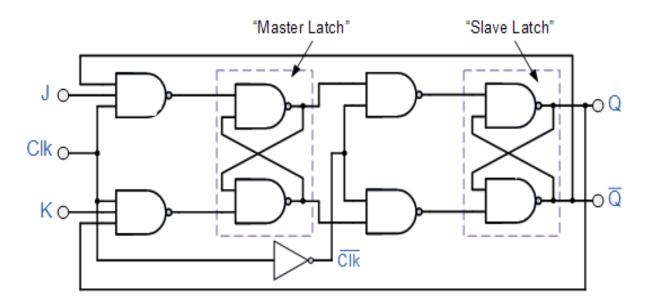

#### Q7. Explain The Master-Slave JK Flip-flop.

Ans. The Master-Slave Flip-Flop is basically two gated SR flip-flops connected together in a series configuration with the slave having an inverted clock pulse. The outputs from Q and Q from the "Slave" flip-flop are fed back to the inputs of the "Master" with the outputs of the "Master" flip-flop being connected to the two inputs of the "Slave" flip-flop. This feedback configuration from the slave's output to the master's input gives the characteristic toggle of the JK flip-flop as shown below.

#### The Master-Slave JK Flip-Flop

The input signals J and K are connected to the gated "master" SR flip-flop which "locks" the input condition while the clock (Clk) input is "HIGH" at logic level "1". As the clock input of the "slave" flip-flop is the inverse (complement) of the "master" clock input, the "slave" SR flip-flop does not toggle. The outputs from the "master" flip-flop are only "seen" by the gated "slave" flip-flop when the clock input goes "LOW" to logic level "0". When the clock is "LOW", the outputs from the "master" flip-flop are latched and any additional changes to its inputs are ignored. The gated "slave" flip-flop now responds to the state of its inputs passed over by the "master" section. Then on the "Low-to-High" transition of the clock pulse the inputs of the "master" flip-flop are fed through to the gated inputs of the "slave" flip-flop and on the "High-to-Low" transition the same inputs are reflected on the output of the "slave" making this type of flip-flop edge or pulse-triggered.

Then, the circuit accepts input data when the clock signal is "HIGH", and passes the data to the output on the falling-edge of the clock signal. In other words, the Master-Slave JK Flip-flop is a "Synchronous" device as it only passes data with the timing of the clock signal.

### Chapter 3

# Register

#### Q1. Explain registers.

**Ans.** It is group of flip flop suitable for storing binary information. Each flip flop is a binary cell capable of storing one bit of information. An n -bit register has a group of n flip flops and is capable of storing any binary information containing n bits. Register mainly used for storing and shifting data entered into it from an external source.

A register capable of shifting its binary information either to the right or to the left is called a "Shift register".

#### Q2. Define the types of Shift Registers.

**Ans.** Shift registers are classified into the following types depending on the way in which the data is entered and retrieved.

**Serial-in to Parallel-out (SIPO)** - the register is loaded with serial data, one bit at a time, with the stored data being available in parallel form.

**Serial-in to Serial-out (SISO)** - the data is shifted serially "IN" and "OUT" of the register, one bit at a time in either a left or right direction under clock control.

**Parallel-in to Serial-out (PISO)** - the parallel data is loaded into the register simultaneously and is shifted out of the register serially one bit at a time under clock control.

**Parallel-in to Parallel-out (PIPO)** - the parallel data is loaded simultaneously into the register, and transferred together to their respective outputs by the same clock pulse.

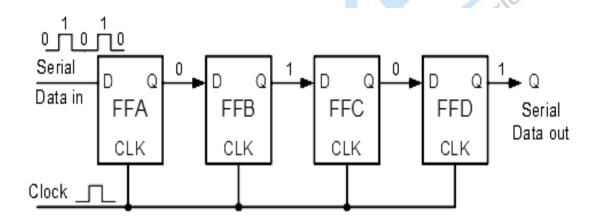

#### Q3. Explain Serial-in to Serial-out (SISO).

**Ans.** This **shift register** is very similar to the SIPO above, except were before the data was read directly in a parallel form from the outputs  $Q_A$  to  $Q_D$ , this time the data is allowed to flow straight through the register and out

of the other end. Since there is only one output, the DATA leaves the shift register one bit at a time in a serial pattern, hence the name **Serial-in to Serial-Out Shift Register** or **SISO**.

The SISO shift register is one of the simplest of the four configurations as it has only three connections, the serial input (SI) which determines what enters the left hand flip-flop, the serial output (SO) which is taken from the output of the right hand flip-flop and the sequencing clock signal (Clk). The logic circuit diagram below shows a generalized serial-in serial-out shift register.

#### 4-bit Serial-in to Serial-out Shift Register

This type of **Shift Register** also acts as a temporary storage device or as a time delay device for the data, with the amount of time delay being controlled by the number of stages in the register, 4, 8, 16 etc or by varying the application of the clock pulses. Commonly available IC's include the 74HC595 8-bit Serial-in/Serial-out Shift Register all with 3-state outputs.

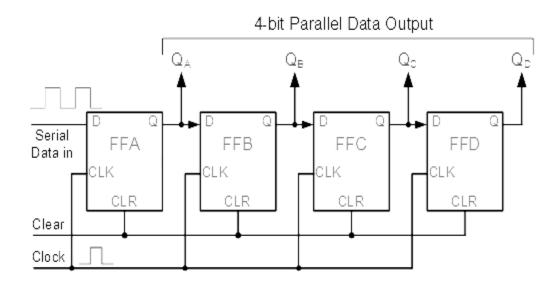

#### Q4. Explain Serial-in to Parallel-out (SIPO).

**Ans.** 4-bit Serial-in to Parallel-out Shift Register

The operation is as follows. Assume that all the flip-flops (FFA to FFD) have just been RESET (CLEAR input) and that all the outputs  $Q_A$  to  $Q_D$  are at logic level "0" i.e, no parallel data output. If a logic "1" is connected to the DATA input pin of FFA then on the first clock pulse the output of FFA and therefore the resulting  $Q_A$  will be set HIGH to logic "1" with all the other outputs still remaining LOW at logic "0". Assume now that the DATA input pin of FFA has returned LOW again to logic "0" giving us one data pulse or 0-1-0.

The second clock pulse will change the output of FFA to logic "0" and the output of FFB and  $Q_B$  HIGH to logic "1" as its input D has the logic "1" level on it from  $Q_A$ . The logic "1" has now moved or been "shifted" one place along the register to the right as it is now at  $Q_A$ . When the third clock pulse arrives this logic "1" value moves to the output of FFC ( $Q_C$ ) and so on until the arrival of the fifth clock pulse which sets all the outputs  $Q_A$  to  $Q_D$  back again to logic level "0" because the input to FFA has remained constant at logic level "0".

The effect of each clock pulse is to shift the data contents of each stage one place to the right, and this is shown in the following table until the complete data value of 0-0-0-1 is stored in the register. This data value can now be read directly from the outputs of  $Q_A$  to  $Q_D$ . Then the data has been converted from a serial data input signal to a parallel data output. The truth table and following waveforms show the propagation of the logic "1" through the register from left to right as follows.

Basic Movement of Data through a Shift Register

| Wovement of Butu | <b>11110 41511 4</b> |    | 813161 |    |  |

|------------------|----------------------|----|--------|----|--|

| Clock Pulse No   | Q.A.                 | QB | QC     | QD |  |

| 0                | 0                    | 0  | 0      | 0  |  |

| 1                | 1                    | 0  | 0      | 0  |  |

| 2                | 0                    | 1  | 0      | 0  |  |

| 3                | 0                    | 0  | 1      | 0  |  |

| 4                | 0                    | 0  | 0      | 1  |  |

| 5                | 0                    | 0  | 0      | 0  |  |

|                  |                      |    |        |    |  |

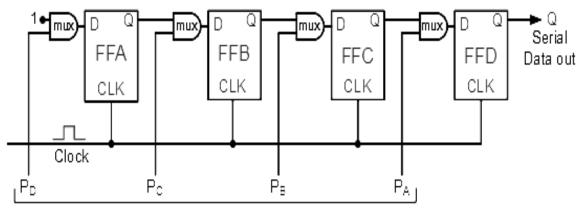

#### Q5. Explain Parallel-in to Serial-out (PISO).

Ans. The Parallel-in to Serial-out shift register acts in the opposite way to the serial-in to parallel-out one above. The data is loaded into the register in a parallel format i.e. all the data bits enter their inputs simultaneously, to the parallel input pins P<sub>A</sub> to P<sub>D</sub> of the register. The data is then read out sequentially in the normal shift-right mode from the register at Q representing the data present at P<sub>A</sub> to P<sub>D</sub>. This data is outputted one bit at a time on each clock cycle in a serial format. It is important to note that with this system a clock pulse is not required to parallel load the register as it is already present, but four clock pulses are required to unload the data.

#### 4-bit Parallel-in to Serial-out Shift Register

4-bit Parallel Data Input

As this type of shift register converts parallel data, such as an 8-bit data word into serial format, it can be used to multiplex many different input lines into a single serial DATA stream which can be sent directly to a computer or transmitted over a communications line. Commonly available IC's include the 74HC166 8-bit Parallel-in/Serial-out Shift Registers.

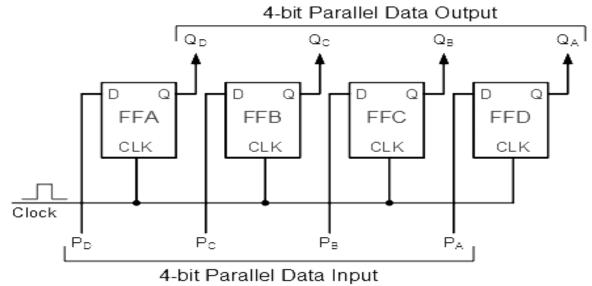

#### Q6. Explain Parallel-in to Parallel-out (PIPO).

Ans. The final mode of operation is the Parallel-in to Parallel-out Shift Register. This type of register also acts as a temporary storage device or as a time delay device similar to the SISO configuration above. The data is presented in a parallel format to the parallel input pins P<sub>A</sub> to P<sub>D</sub> and then transferred together directly to their respective output pins Q<sub>A</sub> to Q<sub>A</sub> by the same clock pulse. Then one clock pulse loads and unloads the register. This arrangement for parallel loading and unloading is shown below.

#### 4-bit Parallel-in to Parallel-out Shift Register

The PIPO shift register is the simplest of the four configurations as it has only three connections, the parallel input (PI) which determines what enters the flip-flop, the parallel output (PO) and the sequencing clock signal (Clk).

Similar to the Serial-in to Serial-out shift register, this type of register also acts as a temporary storage device or as a time delay device, with the amount of time delay being varied by the frequency of the clock pulses. Also, in this type of register there are no interconnections between the individual flip-flops since no serial shifting of the data is required.

## Chapter 4

# I/O Interface

#### Q1. Explain with diagram Memory I/O bus.

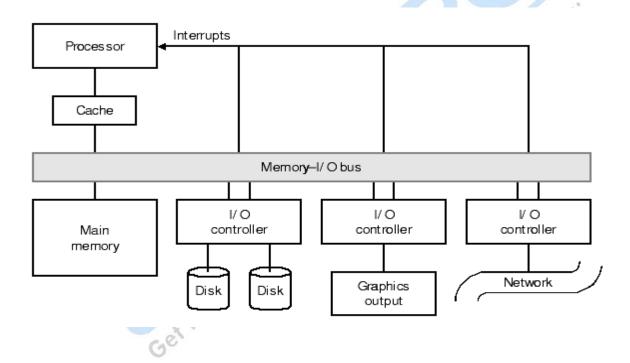

**Ans.** All components of a computer, including CPU, memory, and I/O devices (hard drive, floppy drive, keyboard, mouse, display, etc.) need to be connected by various buses.

Three types of information need to be transmitted between two devices in different lines of the bus: control, data and address. Typically, the control lines include request, grant, release, etc., for the proper communication and coordination of the bus usage by multiple devices.

#### Q2. Explain the ways how peripheral device communicate and Interface.

**Ans.** The operations in I/O devices are much slower than those in the CPU, various methods are used to facilitate the communications.

#### 1. Two ways for CPU to communicate with the I/O devices:

- Memory-mapped I/O: portions of the address space are assigned to the I/O devices, so that the read and write operations involving an I/O device are treated by the CPU in the same way as reading and writing the memory.

- Special I/O instructions: to specify both the device number and the command.

#### 2. Two ways for I/O devices to communicate with the CPU:

o Polling: The I/O device behaves passively.

After receiving command from the CPU, the I/O device carries out the command, e.g., to get some data ready for the CPU to get, and sets a status register. The CPU polls the device periodically by checking this register, and get the data when it indicates the availability of the data.

o Interrupt: The I/O device behaves actively.

When the I/O needs CPU's attention, e.g., some data are ready for CPU to get, it sends an interrupt signal to CPU. The process in CPU is interrupted so that it can attend the I/O's needs. When multiple I/O devices send out interrupts, the one with higher priority will be attended first.

The CPU is interrupted by the mouse controller only when a mouse move is detected.

#### 3. Two ways for data transfer between the memory and I/O:

- CPU controlled: The communication and data transfer between memory and I/O is controlled by the CPU by either polling or interrupt;

- Direct Memory Access (DMA): The communication and data transfer between memory and I/O is controlled by a special

controller. CPU is only interrupted by the I/O device when the transfer is complete or error occurs.

#### Q3. Explain CISC.

A Complex Instruction Set Computer (CISC) supplies a large number of Ans. complex instructions at the assembly language level. Assembly language is which low-level computer programming language in each statement corresponds to a single machine instruction. CISC facilitate the extensive manipulation instructions computational elements and events such as memory, binary arithmetic, and addressing. This particular architectural methodology requires smaller binary files (because each CISC command accomplishes so much, relatively speaking) but involves relatively slow execution of each individual instruction (because the processor must perform more binary manipulations to fulfill each instruction). The goal of the CISC architectural philosophy is to make microprocessors easy and flexible to program and to provide for more efficient memory use. э**е**

#### CISC Problem

- 1.Performance tuning unsuccessful

- Rarely used high-level instructions

- Sometimes slower than equivalent sequence

#### 2. High complexity

- Pipelining bottlenecks → lower clock rates

- Interrupt handling can complicate even more

#### 3.Marketing

■ Prolonged design time and frequent microcode errors hurt competitiveness

#### Q4. Explain RISC.

Ans. Reduced instruction set computing, or RISC, is a CPU design strategy based on the insight that simplified (as opposed to complex) instructions can provide higher performance if this simplicity enables much faster execution of each instruction. A computer based on this strategy is a reduced instruction set computer.

# 1.Low complexity

- Generally results in overall speedup

- Less error-prone implementation by hardwired logic or simple WReldied Queries. microcode.

#### 2.VLSI implementation advantages

- Less transistors

- Extra space: more registers, cache

# 3.Marketing

■ Reduced design time, less errors, and more options increase competitiveness

#### Q5. Define instruction cycle.

during which The time period one instruction is from memory and executed when a computer is given an instruction in machine language.

There are typically four stages of an instruction cycle that the CPU carries out:

- 1. Fetch the instruction from memory. This step brings the instruction into the instruction register, a circuit that holds the instruction so that it can be decoded and executed.

- 2. Decode the instruction.

- 3. Read the effective address from memory if the instruction has an indirect address.

- Execute the instruction. 4.

Steps 1 and 2 are called the *fetch cycle* and are the same for each instruction. Steps 3 and 4 are called the *execute cycle* and will change with each instruction.

The term refers to both the series of four steps and also the amount of time that it takes to carry out the four steps.

An instruction cycle also is called *machine cycle*.

# Q6. Define Instruction Pipeline.

**Ans.** An instruction pipeline is a technique used in the design of modern microprocessors, microcontrollers and CPUs to increase their instruction throughput (the number of instructions that can be executed in a unit of time).

The main idea is to divide the processing of a CPU instruction, as defined by the instruction **microcode**, into a series of independent steps of microoperations, with storage at the end of each step. This allows the CPUs control logic to handle instructions at the processing rate of the slowest step, which is much faster than the time needed to process the instruction as a single step.

The term pipeline refers to the fact that each step is carrying a single microinstruction and each step is linked to another step.

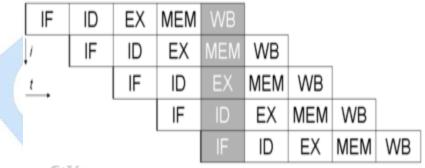

Basic five-stage pipeline in a RISC machine (IF = Instruction Fetch, ID = Instruction Decode, EX = Execute, MEM = Memory access, WB = Register write back). The vertical axis is successive instructions, the horizontal axis is time. So in the green column, the earliest instruction is in WB stage, and the latest instruction is undergoing instruction fetch.

# **Advantages of Pipelining:**

- 1. The cycle time of the processor is reduced; increasing the instruction throughput.

- 2. If pipelining is used, the CPU Arithmetic logic unit can be designed faster, but more complex.

- 3. Pipelining in theory increases performance over an un-pipelined core by a factor of the number of stages and the code is ideal for pipeline execution.

- 4. Pipelined CPUs generally work at a higher clock frequency than the RAM clock frequency, increasing computers overall performance.

# **Disadvantages of Pipelining:**

ed Querit Pipelining has many disadvantages though there are a lot of techniques used by CPUs and compilers designers to overcome most of them of them; following is a list of common drawbacks:

- 1. The design of a non-pipelined processor simpler and cheaper to manufacture, non-pipelined processor executes only a single instruction at a time. This prevents branch delays (in Pipelining, every branch is delayed) as well as problems when serial instructions being executed concurrently.

- 2. In pipelined processor, insertion of flip flops between modules increases the instruction latency compared to a non-pipelined processor.

- 3. A non-pipelined processor will have a defined instruction throughput. The performance of a pipelined processor is much harder to predict and may vary widely for different programs.

# Chapter 5

# **Instruction and Addressing**

# Q1. Explain instruction formats.

**Ans.** An instruction format defines the layout of the bits of ab instruction , in terms of its constituent parts.

The bits of the instruction are divided into groups called fields. The most common fields are:

- An operation code that specifies the operation to be performed.

- An address field that specifies a memory address or register.

- A mode field that tells us how the operand or the effective address of the operand is to be found out.

Opcode-Field Address-Field

- Op-field: specifies the operation to be performed;

- Address-field: provides operands or the CPU register/MM addresses of the operands.

# Q2. What are the types of instruction formats. Explain with e.g.

**Ans.** 1. Three address instructions

- 2. Two address instructions

- 3. One address instructions

- 4. Zero address instruction

#### Three address instructions

Computers with three address instructions use three address fields to specify either a processor register or a memory operand

Example: X = (A+B)\*C+D

where A, B, C, D and X are five main memory locations representing five variables;

3-address format:

Assume variables A, B, C, D, and X are stored in MM locations labeled by their names.

ADD R1, A, B

$$R1 \leftarrow M[A] + M[B]$$

ADD R2,C,D  $R2 \leftarrow M[C] + M[D]$

MUL X,R1,R2  $M[X] \leftarrow R1*R2$

Note: here we assume an instruction OP dst src1 src2 means:-

$$dst \leftarrow [src1]*[src2]$$

where src1 and src2 are the *source operand*, dst is the *destination operand*, and \* represents the operation specified in Op-code field OP.

#### Two address instructions

Computers that use this type of instruction have two addresses specified in their instructions

Example: X = (A+B)\*C+D

MOV R1, A R1

$$\leftarrow$$

[A]

ADD R1, B R1  $\leftarrow$  [B] + [R1]

MOV R2, C R2  $\leftarrow$  [C]

ADD R2, D R2  $\leftarrow$  [D] + [R2]

MUL R2, R1 R2  $\leftarrow$  [R1] \* [R2]

MOV X,R2 X  $\leftarrow$  [R2]

Note: here we assume an instruction OP dst src means:-

$$dst \leftarrow [dst]*[src]$$

where src is the *source operand*, dst is the *destination operand*, and \* represents the operation specified in Op-code field OP.

#### One address instructions

Always use an implied accumulator (AC).

| LOAD  | A | # | $AC \leftarrow [A]$             |

|-------|---|---|---------------------------------|

| ADD   | В | # | $AC \leftarrow [AC] + [B]$      |

| STORE | R | # | $R \leftarrow [AC]$             |

| LOAD  | C | # | $AC \leftarrow [C]$             |

| ADD   | D | # | $AC \leftarrow [AC] + [D]$      |

| MUL   | R | # | $AC \leftarrow [AC] \times [R]$ |

| STORE | X | # | $X \leftarrow [AC]$             |

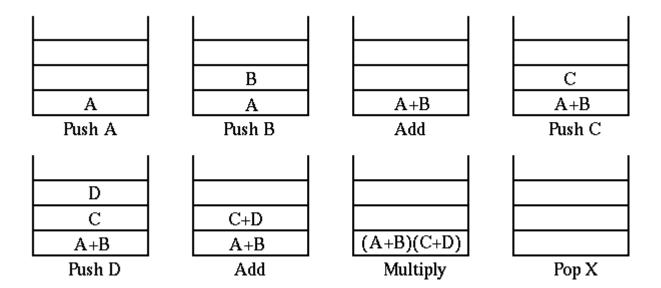

# Zero address instructions

used in stack-organized computer.

First, the give First, the given notation of the operation is converted into "reversed Polish notation (RPN)"

$$(A+B) \times (C+D) \Longrightarrow AB + CD + \times$$

then execute this program:

**PUSH** Α В **PUSH** ADD

| PUSH | C |

|------|---|

| PUSH | D |

| ADD  |   |

| MUL  |   |

| POP  | X |

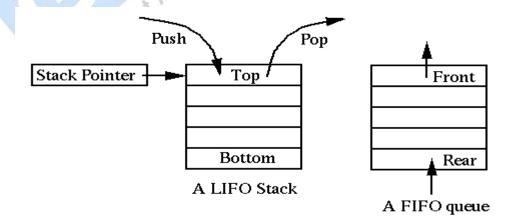

- Stack A last-in, first-out (LIFO) data structure.

- o Queue A first-in, first-out (FIFO) data structure.

#### Q3. What are the Addressing modes.

**Ans.** The addressing mode specifies a rule for interpreting or modifying the address field of the instruction.

# Types of Addressing Modes:-

- Implied addressing mode

- Immediate addressing mode

- •Direct addressing mode

- Indirect addressing mode

- Register addressing mode

- Register Indirect addressing mode

- Auto increment or Auto decrement addressing mode

- Relative addressing mode

- Indexed addressing mode

- Base register addressing mode

| •Indirect addressing mode                                                                                                                                                                                                                                   |                             |                                         |                                                             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------|-------------------------------------------------------------|--|--|--|

| • Register addressing mode                                                                                                                                                                                                                                  |                             |                                         |                                                             |  |  |  |

| Register Indirect addressing mode                                                                                                                                                                                                                           |                             |                                         |                                                             |  |  |  |

| Auto increment or Auto decrement addressing mode                                                                                                                                                                                                            |                             |                                         |                                                             |  |  |  |

| •Relative addressing mode                                                                                                                                                                                                                                   |                             |                                         |                                                             |  |  |  |

| •Indexed addressing mode                                                                                                                                                                                                                                    |                             |                                         |                                                             |  |  |  |

| Base register addressing mode                                                                                                                                                                                                                               |                             |                                         |                                                             |  |  |  |

| <ul> <li>Register addressing mode</li> <li>Register Indirect addressing mode</li> <li>Auto increment or Auto decrement addressing mode</li> <li>Relative addressing mode</li> <li>Indexed addressing mode</li> <li>Base register addressing mode</li> </ul> |                             |                                         |                                                             |  |  |  |

| Addressing<br>Modes                                                                                                                                                                                                                                         |                             | to John S                               |                                                             |  |  |  |

|                                                                                                                                                                                                                                                             | Example<br>Instruction      | Meaning                                 | When used                                                   |  |  |  |

| Register                                                                                                                                                                                                                                                    |                             | Meaning<br>R4 <- R4 + R3                | When used When a value is in a register                     |  |  |  |

|                                                                                                                                                                                                                                                             | Instruction                 |                                         | When a value                                                |  |  |  |

| Register                                                                                                                                                                                                                                                    | Add R4,R3                   | R4 <- R4 + R3                           | When a value<br>is in a register                            |  |  |  |

| Register Immediate                                                                                                                                                                                                                                          | Add R4,R3 Add R4,#3 Add R4, | R4 <- R4 + R3  R4 <- R4 + 3  R4 <- R4 + | When a value is in a register For constants Accessing local |  |  |  |

|                    | (R1 + R2)              | M[R1+R2]                        | addressing:<br>R1 - base of<br>array<br>R2 - index<br>amount                             |

|--------------------|------------------------|---------------------------------|------------------------------------------------------------------------------------------|

| Direct             | Add R1,<br>(1001)      | R1 <- R1 + M[1001]              | Useful in accessing static data                                                          |

| Memory<br>deferred | Add R1,<br>@(R3)       | R1 <- R1 + M[M[R3]]             | If R3 is the address of a pointer <i>p</i> , then mode yields * <i>p</i>                 |

| Auto-<br>increment | Add R1,<br>(R2)+       | R1 <- R1 +M[R2]<br>R2 <- R2 + d | Useful for stepping through arrays in a loop. R2 - start of array d - size of an element |

| Auto-<br>decrement | Add R1,-<br>(R2)       | 10                              | Same as autoincrement. Both can also be used to implement a stack as push and pop        |

| Scaled             | Add R1,<br>100(R2)[R3] |                                 | Used to index arrays. May be applied to any base addressing mode in some machines.       |

# Q4. What is assembly language?

Ans. An assembly language is a low-level programming language for computers, microprocessors, microcontrollers, and programmable devices. It implements a symbolic representation of codes and the machine other constants needed to program given CPU architecture. This representation is usually defined by the hardware manufacturer, and is based on mnemonics that symbolize processing steps (instructions), processor registers, memory locations, and other language features. An assembly language is thus specific to a certain physical (or virtual) computer architecture. This is in contrast most high-level programming languages.

#### Q5. Define Assembler

Ans. Assembler creates object code by translating assembly instruction mnemonics into opcodes, and by resolving symbolic names for memory locations and other entities The use of symbolic references is a key feature of assemblers, saving tedious calculations and manual address updates after program modifications. Most assemblers also include macro facilities for performing textual substitution—e.g., to generate common short sequences of instructions as inline, instead of called subroutines.

# Q6. Explain the Number of passes of an assembler.

**Ans.** There are two types of assemblers based on how many passes through the source are needed to produce the executable program.

- One-pass assemblers go through the source code once. Any symbol used before it is defined will require "errata" at the end of the object code telling the linker or the loader to "go back" and overwrite a placeholder which had been left where the as yet undefined symbol was used.

- Two-pass assemblers create a table with all symbols and their values in the first pass, then use the table in a second pass to generate code.

- In both cases, the assembler must be able to determine the size of each instruction on the first or only pass in order to calculate the addresses of symbols. This means that if the size of an operation referring to an

operand defined later depends on the type or distance of the operand, the assembler will make a pessimistic estimate when first encountering the operation, and if necessary pad it with one or more "no-operation" instructions in the second pass or the errata.

The original reason for the use of one-pass assemblers was speed of assembly; however, modern computers perform two-pass assembly without unacceptable delay. The advantage of the two-pass assembler is that the absence of a need for errata makes the linker (or the loader if the assembler directly produces executable code) simpler and faster

# Q7. Explain Assembly directives.

Ans. Assembly directives, also called pseudo opcodes, pseudo-operations or pseudo-ops, are instructions that are executed by an assembler at assembly time, not by a CPU at run time. They can make the assembly of the program dependent on parameters input by a programmer, so that one program can be assembled different ways, perhaps for different applications. They also can be used to manipulate presentation of a program to make it easier to read and maintain.

#### Q8. Explain Pseudo instructions.

Ans. Pseudo instructions means "fake instruction". When designing a modern ISA, one criteria is to decide whether an instruction should be part of the ISA or not. Initially, a use for the instruction, it was often added to their instruction set. This lead to bloated and slow implementations.

By taking out some instructions, assembly language programmers would find it a little harder to write code. To make it easier for them, pseudo instructions were added. Pseudo instructions do not correspond to real MIPS instructions.

Instead, the assembler, a program that converts assembly language programs to machine code, would then translate pseudo instructions to real instructions, usually requiring at least one on more instructions.

Pseudo instructions not only make it easier to program, it can also add clarity to the program, by making the intention of the programmer more clear.

# Q9. Explain Macro Instruction.

Ans. A macro instruction is a line of computer program coding that results in one or more lines of program coding in the target programming language, sets variables for use by other statements, etc.. In the mid 1950s, when assembly language programming was commonly used to write programs for digital computers, the use of macro instructions was initiated for two main purposes: to reduce the amount of program coding that had to be written by generating several assembly language statements from one macro instruction and to enforce program writing standards, e.g. specifying input/output commands in standard ways. Macro instructions were effectively a middle step between assembly language programming and the high-level programming languages that followed, such as FORTRAN and COBOL.

# Q.10 Explain linking and loading

**Ans.** Linking and Loading

**Loading** is the process of copying an executable image into memory.

- \* more sophisticated loaders are able to relocate images to fit into available memory

- \* must readjust branch targets, load/store addresses

**Linking** is the process of resolving symbols between independent object files.

- \* suppose we define a symbol in one module, and want to use it in another

- \* some notation, such as .EXTERNAL, is used to tell assembler that a symbol is defined in another module

- \* linker will search symbol tables of other modules to resolve symbols and complete code generation before loading

# Chapter 6

# Arithmetic/Logic unit

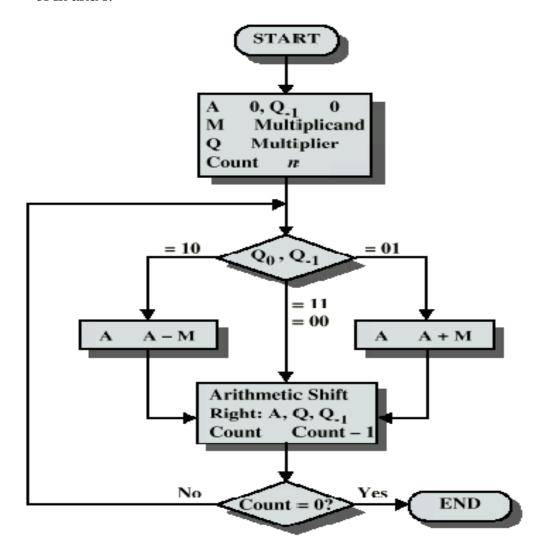

# Q1. Explain Booth's Algo.

- **Ans.** Booth's multiplication algorithm is a multiplication algorithm that multiplies two signed binary numbers in two's complement notation. Booth's algorithm involves repeatedly adding one of two predetermined values *A* and *S* to a product *P*, then performing a rightward arithmetic shift on *P*. Let **m** and **r** be the multiplicand and multiplier, respectively; and let *x* and *y* represent the number of bits in **m** and **r**.

- 1. Determine the values of A and S, and the initial value of P. All of these numbers should have a length equal to (x + y + 1).

- 1. A: Fill the most significant (leftmost) bits with the value of  $\mathbf{m}$ . Fill the remaining (y + 1) bits with zeros.

- 2. S: Fill the most significant bits with the value of  $(-\mathbf{m})$  in two's complement notation. Fill the remaining (y + 1) bits with zeros.

- 3. P: Fill the most significant *x* bits with zeros. To the right of this, append the value of **r**. Fill the least significant (rightmost) bit with a zero.

- 2. Determine the two least significant (rightmost) bits of *P*.

- 1. If they are 01, find the value of P + A. Ignore any overflow.

- 2. If they are 10, find the value of P + S. Ignore any overflow.

- 3. If they are 00, do nothing. Use *P* directly in the next step.

- 4. If they are 11, do nothing. Use *P* directly in the next step.

- 3. Arithmetically shift the value obtained in the 2nd step by a single place to the right. Let *P* now equal this new value.

- 4. Repeat steps 2 and 3 until they have been done *y* times.

5. Drop the least significant (rightmost) bit from *P*. This is the product of **m** and **r**.

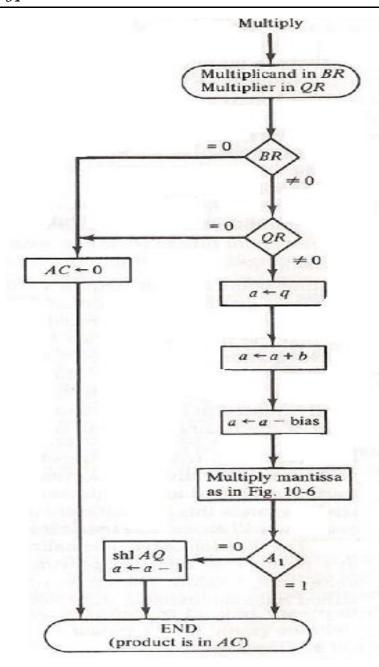

Booth's algo for two's complement multiplication

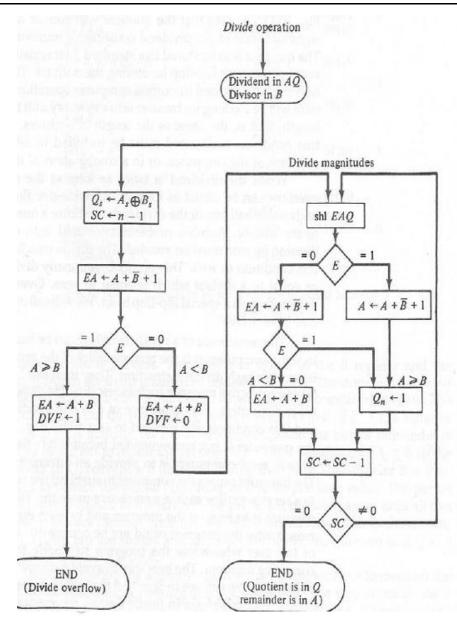

# Q2. Explain division algorithm. Ans

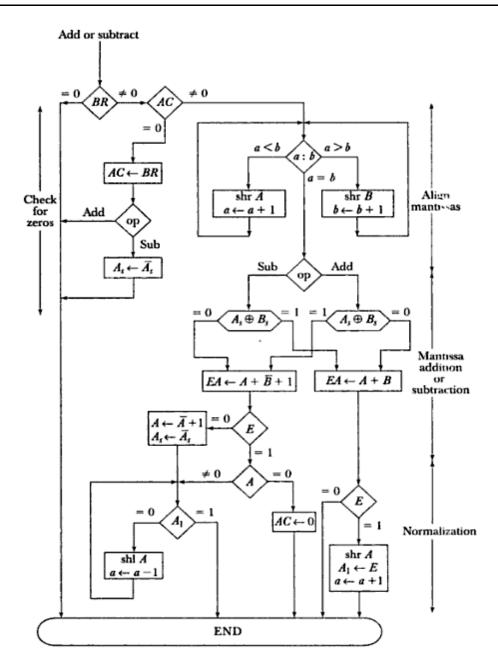

Q3. Explain with flowchart addition and subtraction of floating point numbers.

Ans.

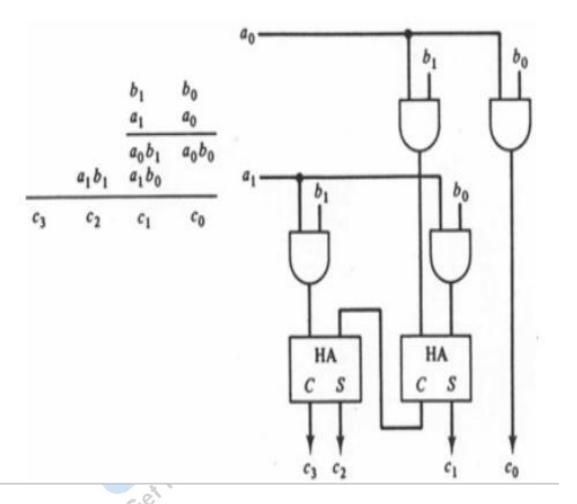

# Q4. Explain array multiplier.

**Ans.** It is a Combination circuit, Requires large number of gates. Its product generated in one micro operation

- Became feasible after integrated circuits developed

- Needed for j multiplier and k multiplicand bits

- "jxk AND gates

- " j 1 k-bit adders to produce product of j + k bit

2-bit by 2-bit Array Multiplier

# Q5. Explain Multiplication of floating point numbers. Ans.

d Queries...

# Chapter 7

# Memory

# Q1. Explain Ram and Rom Chip

Ans. Random access memory, a type of computer memory that can be accessed randomly; that is, any byte of memory can be accessed without touching the preceding bytes. RAM is the most common type of memory found in computers and other devices, such as printers.

There are two different types of RAM: DRAM (dynamic random access memory) and SRAM (static random access memory).

The two types differ in the technology they use to hold data, with dram being the more common type. In terms of speed, SRAM is faster. DRAM needs to be refreshed thousands of times per second while SRAM does not need to be refreshed, which is what makes it faster than DRAM. DRAM supports access times of about 60 nanoseconds, SRAM can give access times as low as 10 nanoseconds. Despite SRAM being faster, it's not as commonly used as dram because it's so much more expensive. Both types of RAM are *volatile*, meaning that they lose their contents when the power is turned off.

*Read-only memory*, computer memory on which data has been prerecorded. Once data has been written onto a ROM chip, it cannot be removed and can only be read. Unlike main memory (RAM), ROM retains its contents even when the computer is turned off. ROM is referred to as being *nonvolatile*, whereas RAM is *volatile*.

# Q2. Explain auxiliary memory.

Ans. Auxiliary memory units are among computer peripheral equipment. They trade slower access rates for greater storage capacity and data stability. Auxiliary memory holds programs and data for future use, and, because it is nonvolatile (like ROM), it is used to store inactive programs and to archive data. Early forms of auxiliary storage included punched

paper tape, punched cards, and magnetic drums. the most common forms of auxiliary storage have been magnetic disks, magnetic tapes, and optical discs.

Magnetic tape

Magnetic tape, similar to the tape used in tape recorders, has also been used for auxiliary storage, primarily for archiving data. Tape is cheap, but access time is far slower than that of a magnetic disk because it is sequential-access memory—i.e., data must be sequentially read and written as a tape is unwound, rather than retrieved directly from the desired point on the tape.

Optical discs

Another form of largely read-only memory is the optical compact disc, developed from videodisc technology during the early 1980s. Data are recorded as tiny pits in a single spiral track on plastic discs that range from 3 to 12 inches (7.6 to 30 cm) in diameter, though a diameter of 4.8 inches (12 cm) is most common.

# Q3. Explain cache memory.

Ans. The *cache* is a small amount of high-speed memory, usually with a memory cycle time comparable to the time required by the CPU to fetch one instruction. The cache is usually filled from main memory when instructions or data are fetched into the CPU. Often the main memory will supply a wider data word to the cache than the CPU requires, to fill the cache more rapidly. The amount of information which is replaces at one time in the cache is called the *line size* for the cache. This is normally the width of the data bus between the cache memory and the main memory.

# Q4. Explain the working of cache memory

Ans. When the *processor* needs to read or write a location in main memory, it first checks whether that memory location is in the cache. This is accomplished by comparing the address of the memory location to all tags in the cache that might contain that address. If the processor finds that the memory location is in the cache, we say that a *cache hit* has occurred; otherwise, we speak of a *cache miss*. In the case of a cache hit, the processor immediately reads or writes the data in the cache line. The proportion of accesses that result in a cache hit is known as the *hit rate*, and is a measure of the effectiveness of the cache for a given program or algorithm.

In the case of a miss, the cache allocates a new entry, which comprises the tag just missed and a copy of the data. The reference can then be applied to the new entry just as in the case of a hit. Read misses delay execution because they require data to be transferred from a much slower memory than the cache itself. Write misses may occur without such penalty since the data can be copied in the background.

In order to make room for the new entry on a cache miss, the cache has to *evict* one of the existing entries. The heuristic that it uses to choose the entry to evict is called the *replacement policy*. The fundamental problem with any replacement policy is that it must predict which existing cache entry is least likely to be used in the future. One popular replacement policy, LRU, replaces the least recently used entry. Defining some memory ranges non *cacheable* avoids affecting performance by storing in caches information which are never re-used or seldom used. Cache misses are simply ignored for not cacheable data. Cache entries may also be disabled or locked depending on the context.

If data are written to the cache, they must at some point be written to main memory as well. The timing of this write is controlled by what is known as the *write policy*. In a *write-through* cache, every write to the cache causes a write to main memory. Alternatively, in a *write-back* or *copy-back* cache, writes are not immediately mirrored to the main memory. Instead, the cache tracks which locations have been written over (these locations are marked *dirty*). The data in these locations are written back to the main memory when that data is evicted from the cache. For this reason, a miss in a write-back cache may sometimes require *two* memory accesses to service: one to first write the dirty location to memory and then another to read the new location from memory.

There are intermediate policies as well. The cache may be write-through, but the writes may be held in a store data queue temporarily, usually so that multiple stores can be processed together (which can reduce bus turnarounds and so improve bus utilization).

# Q5. Explain Virtual memory.

**Ans.** In computing, virtual memory is a memory management technique developed for multitasking kernels. This technique virtualizes a computer architecture's various forms of computer data storage (such as random-access memory and disk storage), allowing a program to be *designed as*

*though* there is only one kind of memory, "virtual" memory, which behaves like directly addressable read/write memory (RAM).

Most modern operating systems that support virtual memory also run each process in its own dedicated address space, allowing a program to be *designed as though*t has sole access to the virtual memory.

Systems that employ virtual memory:

- -use hardware memory more efficiently than do systems without virtual memory.

- -make the programming of applications easier:

- -by hiding fragmentation,

- -by delegating to the kernel the burden of managing the memory hierarchy (there is no need for the program to handle overlays explicitly), -and, when each process is run in its own dedicated address space, by obviating the need to relocate program code or to access memory with relative addressing.

Memory virtualization is a generalization of the concept of virtual memory.

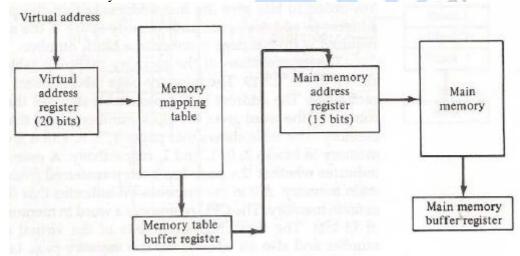

Memory table for mapping virtual address

# Q6. Explain Paging.

Ans. Paging is a memory management technique which widely uses virtual memory concept. When paging is used, the processor divides the linear address space into fixed-size pages (of 4KBytes, 2 MBytes, or 4 MBytes in length) that can be mapped into physical memory and/or disk storage.

When a program (or task) references a logical address in memory, the processor translates the address into a linear address and then uses its paging mechanism to translate the linear address into a corresponding physical address

The main functions of paging are performed when a program tries to access pages that are not currently mapped to physical memory (RAM). This situation is known as a page fault. The operating system must then take control and handle the page fault, in a manner invisible to the program. Therefore, the operating system must:

- -Determine the location of the data in auxiliary storage.

- -Obtain an empty page frame in RAM to use as a container for the data.

- -Load the requested data into the available page frame.

- -Update the page table to show the new data.

- -Return control to the program, transparently retrying the instruction that caused the page fault.

Until there is not enough RAM to store all the data needed, the process of obtaining an empty page frame does not involve removing another page from RAM. If all page frames are non-empty, obtaining an empty page frame requires choosing a page frame containing data to empty. If the data in that page frame has been modified since it was read into RAM (i.e., if it has become "dirty"), it must be written back to its location in secondary storage before being freed; otherwise, the contents of the page's page frame in RAM are the same as the contents of the page in secondary storage, so it does not need to be written back to secondary storage. If a reference is then made to that page, a page fault will occur, and an empty page frame must be obtained and the contents of the page in secondary storage again read into that page frame.

Efficient paging systems must determine the page frame to empty by choosing one that is least likely to be needed within a short time. There are various page replacement algorithms that try to do this. Most operating systems use some approximation of the least recently used (LRU) page replacement algorithm (the LRU itself cannot be implemented on the current hardware) or a working set-based algorithm.

To further increase responsiveness, paging systems may employ various strategies to predict which pages will be needed soon. Such systems will attempt to load pages into main memory preemptively, before a program references them.

# **Chapter 8**

# **Processor**

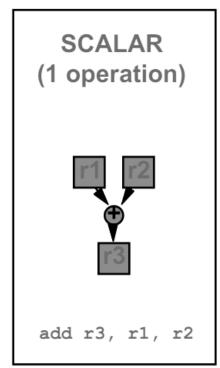

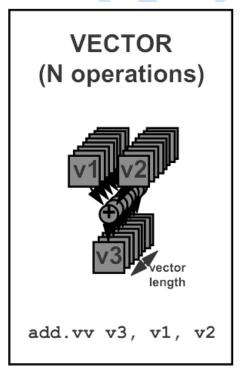

# Q1. Explain vector processors.

**Ans.** Vector processors have high-level operations that work on linear arrays of numbers: "vectors"

Properties of Vector Processors:-

- Each result independent of previous result

- => long pipeline, compiler ensures no dependencies

- => high clock rate

- Vector instructions access memory with known pattern

- => highly interleaved memory

- => amortize memory latency of over » 64 elements

- => no (data) caches required! (Do use instruction cache)

- Reduces branches and branch problems in pipelines

- Single vector instruction implies lots of work (» loop)

- => fewer instruction fetches

Styles of Vector Architectures:-

- memory-memory vector processors: all vector operations are memory to memory

- vector-register processors: all vector operations between vector registers.

# Q2. Explain array processing.

**Ans.** Array processing is signal processing of the outputs of an array of sensors to:

Enhance the signal-to-interference-plus-noise ratio (SINR) compared to that of a single sensor using conventional or adaptive beam forming. Determine the number of emitting sources, the locations of these sources, their waveforms, and other signal parameters. Track multiple moving sources. Array processing is used in radar, sonar, seismic exploration, anti-jamming and wireless communications. One of the main advantages of using array processing along with an array of sensors is a smaller footprint. The problems associated with array processing include the number of sources used, their direction of arrivals, and their signal waveforms.<sup>[1]</sup> There are four assumptions in array processing. The first assumption is that there is uniform propagation in all directions of isotropic and no dispersive medium. The second assumption is that for far field array processing, the radius of propagation is much greater than size of the array and that there is plane wave propagation. The third assumption is that there is a zero mean white noise and signal, which shows uncorrelation. Finally, the last assumption is that there is no coupling and the calibration is perfect.

# Q3. What is multiprocessing?

**Ans.** Multiprocessing is the use of two or more central processing units (CPUs) within a single computer system. The term also refers to the ability of a system to support more than one processor and/or the ability to allocate tasks between them.<sup>[1]</sup> There are many variations on this basic theme, and

the definition of multiprocessing can vary with context, mostly as a function of how CPUs are defined (multiple cores on one die, multiple dies in one package, multiple packages in one system unit, etc.).

Multiprocessing sometimes refers to the execution of multiple concurrent software processes in a system as opposed to a single process at any one instant. However, the terms multitasking or multiprogramming are more appropriate to describe this concept, which is implemented mostly in software, whereas multiprocessing is more appropriate to describe the use of multiple hardware CPUs. A system can be both multiprocessing and multiprogramming, only one of the two, or neither of the two of them.

# Software implementation issues:-

In a single instruction stream, single data stream computer one processor sequentially processes instructions, each instruction processes one data item. One example is the "von Neumann" architecture with RISC.

# 1. SIMD multiprocessing

In a single instruction stream, multiple data stream computer one processor handles a stream of instructions, each one of which can perform calculations in parallel on multiple data locations.

SIMD multiprocessing is well suited to parallel or vector processing, in which a very large set of data can be divided into parts that are individually subjected to identical but independent operations. A single instruction stream directs the operation of multiple processing units to perform the same manipulations simultaneously on potentially large amounts of data.

For certain types of computing applications, this type of architecture can produce enormous increases in performance, in terms of the elapsed time required to complete a given task. However, a drawback to this architecture is that a large part of the system falls idle when programs or system tasks are executed that cannot be divided into units that can be processed in parallel.

SIMD multiprocessing finds wide use in certain domains such as computer simulation, but is of little use in general-purpose desktop and business computing environments.

#### 2. MISD multiprocessing

MISD multiprocessing offers mainly the advantage of redundancy, since multiple processing units perform the same tasks on the same data, reducing the chances of incorrect results if one of the units fails. MISD architectures may involve comparisons between processing units to detect failures. Apart from the redundant and fail-safe character of this type of multiprocessing, it has few advantages, and it is very expensive. It does not improve performance. It can be implemented in a way that is transparent to software. It is used in array processors and is implemented in fault tolerant machines.

# 3. MIMD multiprocessing

MIMD multiprocessing architecture is suitable for a wide variety of tasks in which completely independent and parallel execution of instructions touching different sets of data can be put to productive use. For this reason, and because it is easy to implement, MIMD predominates in multiprocessing.

Processing is divided into multiple threads, each with its own hardware processor state, within a single software-defined process or within multiple processes. Insofar as a system has multiple threads awaiting dispatch (either system or user threads), this architecture makes good use of hardware resources.

MIMD does raise issues of deadlock and resource contention, however, since threads may collide in their access to resources in an unpredictable way that is difficult to manage efficiently. MIMD requires special coding in the operating system of a computer but does not require application changes unless the programs themselves use multiple threads (MIMD is transparent to single-threaded programs under most operating systems, if the programs do not voluntarily relinquish control to the OS). Both system and user software may need to use software constructs such as *semaphores* (also called *locks* or *gates*) to prevent one thread from interfering with another if they should happen to cross paths in referencing the same data. This gating or locking process increases code complexity, lowers performance, and greatly increases the amount of testing required, although not usually enough to negate the advantages of multiprocessing.

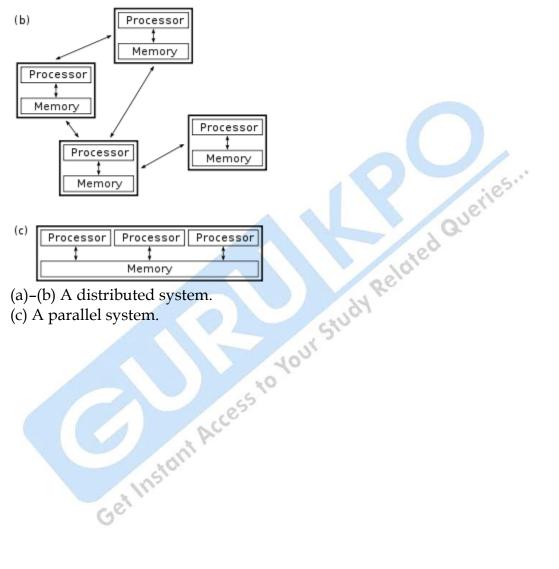

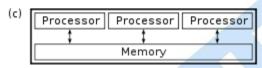

# Q4. Explain distributed computing.

**Ans.** Distributed computing is a field of computer science that studies distributed systems. A distributed system consists of multiple autonomous computers that communicate through a computer network. The computers interact with each other in order to achieve a common

goal. A computer program that runs in a distributed system is called a distributed program, and distributed programming is the process of writing such programs.

Distributed computing also refers to the use of distributed systems to solve computational problems. In distributed computing, a problem is divided into many tasks, each of which is solved by one or more computers.

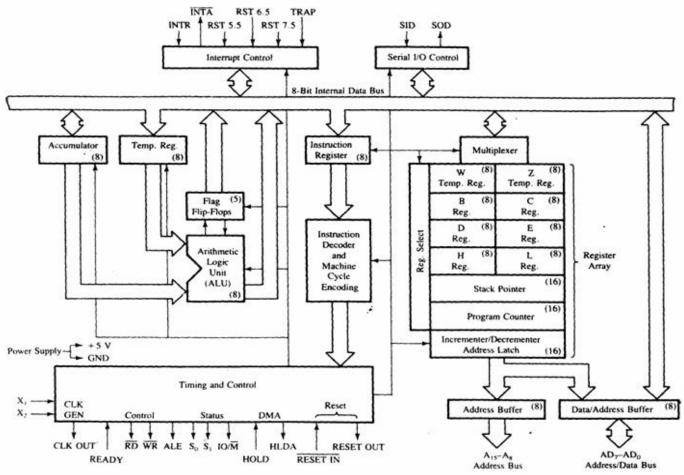

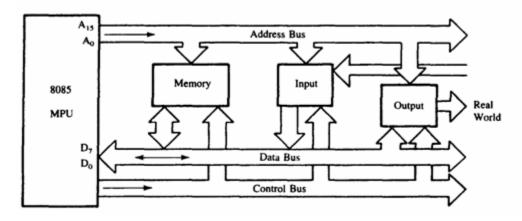

The word distributed in terms such as "distributed system", "distributed programming", and "distributed algorithm" originally referred to computer networks where individual computers were physically distributed within some geographical area. Distributed systems are groups of networked computers, which have the same goal for their work. The terms "concurrent computing", "parallel computing", and "distributed computing" have a lot of overlap, and no clear distinction exists between them. The same system may be characterized both as "parallel" and "distributed"; the processors in a typical distributed system run concurrently in parallel. Parallel computing may be seen as a particular tightly-coupled form of distributed computing, and distributed computing may be seen as a loosely-coupled form of parallel computing. Nevertheless, it is possible to roughly classify concurrent systems as "parallel" or "distributed" using the following criteria: